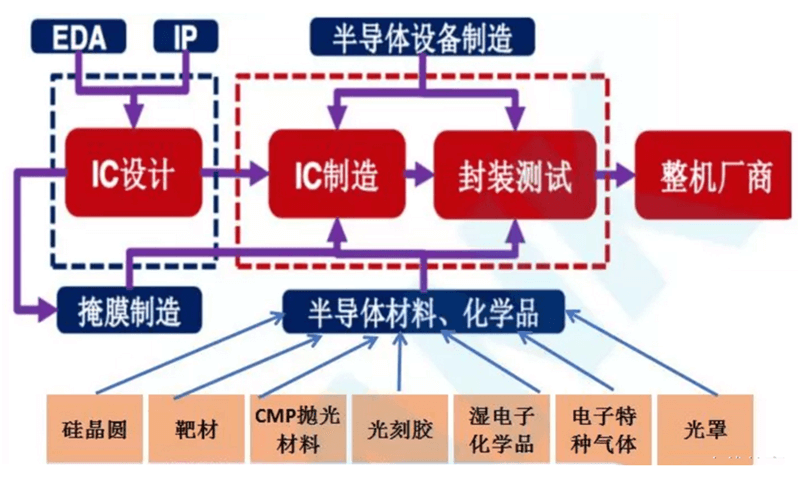

Xét về mặt chuyên môn, quy trình sản xuất chip cực kỳ phức tạp và tốn công sức. Tuy nhiên, xét về toàn bộ chuỗi công nghiệp IC, quy trình này chủ yếu được chia thành bốn giai đoạn: Thiết kế IC → Sản xuất IC → Đóng gói → Kiểm tra.

Quy trình sản xuất chip:

1. Thiết kế chip

Chip là sản phẩm có kích thước nhỏ nhưng độ chính xác cực kỳ cao. Để tạo ra một con chip, thiết kế là khâu đầu tiên. Thiết kế chip đòi hỏi sự hỗ trợ của thiết kế chip, thiết kế chip cần thiết để xử lý với sự trợ giúp của công cụ EDA và một số lõi IP.

Quy trình sản xuất chip:

1. Thiết kế chip

Chip là sản phẩm có kích thước nhỏ nhưng độ chính xác cực kỳ cao. Để tạo ra một con chip, thiết kế là khâu đầu tiên. Thiết kế chip đòi hỏi sự hỗ trợ của thiết kế chip, thiết kế chip cần thiết để xử lý với sự trợ giúp của công cụ EDA và một số lõi IP.

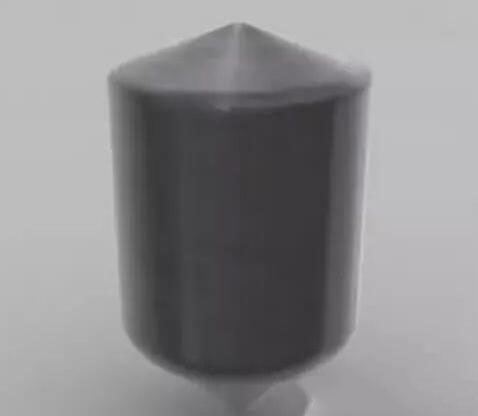

3. Nâng silicon

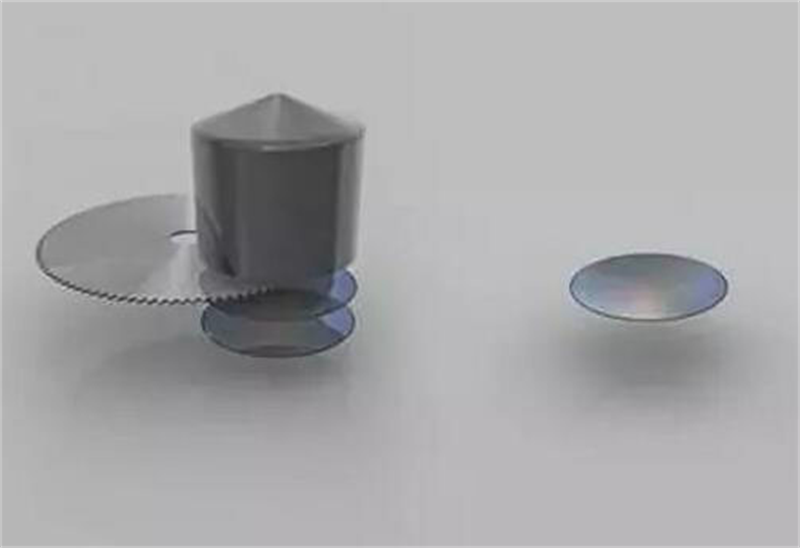

Sau khi tách silic, các vật liệu còn lại bị loại bỏ. Silic tinh khiết trải qua nhiều bước đã đạt đến chất lượng sản xuất bán dẫn. Đây được gọi là silic điện tử.

4. Thỏi đúc silicon

Sau khi tinh chế, silic được đúc thành thỏi silic. Một tinh thể silic cấp điện tử sau khi đúc thành thỏi nặng khoảng 100 kg, độ tinh khiết của silic đạt 99,9999%.

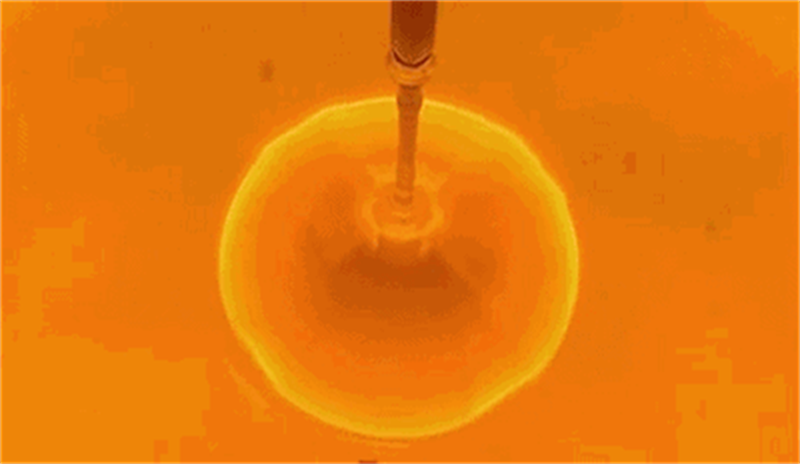

5. Xử lý tập tin

Sau khi đúc thỏi silicon, toàn bộ thỏi silicon phải được cắt thành từng mảnh, đó chính là wafer mà chúng ta thường gọi là wafer, rất mỏng. Sau đó, wafer được đánh bóng cho đến khi hoàn hảo, bề mặt nhẵn mịn như gương.

Đường kính của wafer silicon là 8 inch (200mm) và 12 inch (300mm). Đường kính càng lớn, chi phí cho một chip đơn càng thấp, nhưng độ khó xử lý càng cao.

5. Xử lý tập tin

Sau khi đúc thỏi silicon, toàn bộ thỏi silicon phải được cắt thành từng mảnh, đó chính là wafer mà chúng ta thường gọi là wafer, rất mỏng. Sau đó, wafer được đánh bóng cho đến khi hoàn hảo, bề mặt nhẵn mịn như gương.

Đường kính của wafer silicon là 8 inch (200mm) và 12 inch (300mm). Đường kính càng lớn, chi phí cho một chip đơn càng thấp, nhưng độ khó xử lý càng cao.

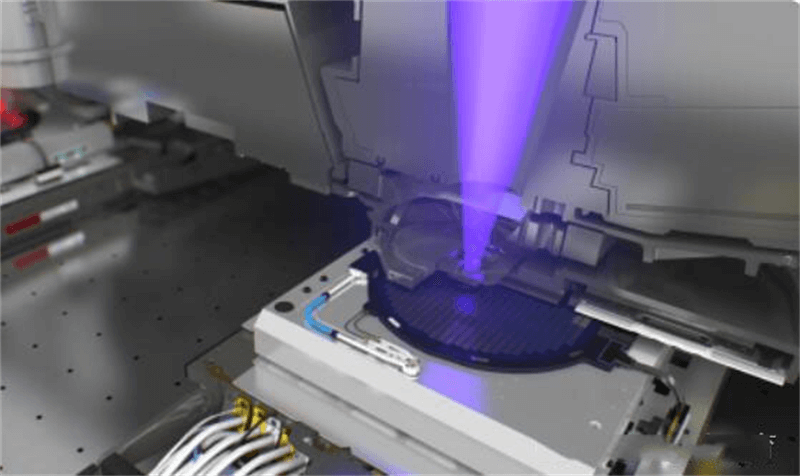

7. Eclipse và tiêm ion

Đầu tiên, cần phải ăn mòn lớp oxit silic và nitrit silic tiếp xúc bên ngoài lớp cản quang, sau đó kết tủa một lớp silic để cách điện giữa ống tinh thể, sau đó sử dụng công nghệ khắc để lộ lớp silic bên dưới. Tiếp theo, bơm boron hoặc phốt pho vào cấu trúc silic, sau đó đổ đầy đồng để kết nối với các bóng bán dẫn khác, rồi phủ thêm một lớp keo nữa để tạo thành một lớp cấu trúc. Nhìn chung, một con chip bao gồm hàng chục lớp, giống như những con đường cao tốc đan xen dày đặc.

7. Eclipse và tiêm ion

Đầu tiên, cần phải ăn mòn lớp oxit silic và nitrit silic tiếp xúc bên ngoài lớp cản quang, sau đó kết tủa một lớp silic để cách điện giữa ống tinh thể, sau đó sử dụng công nghệ khắc để lộ lớp silic bên dưới. Tiếp theo, bơm boron hoặc phốt pho vào cấu trúc silic, sau đó đổ đầy đồng để kết nối với các bóng bán dẫn khác, rồi phủ thêm một lớp keo nữa để tạo thành một lớp cấu trúc. Nhìn chung, một con chip bao gồm hàng chục lớp, giống như những con đường cao tốc đan xen dày đặc.

Thời gian đăng: 08-07-2023