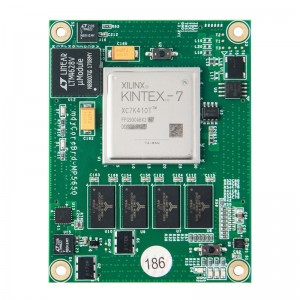

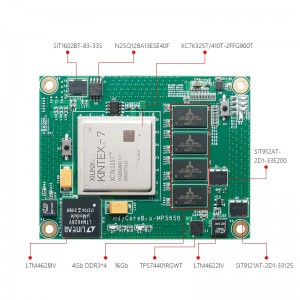

FPGA XILINX-K7 KINTEX7 XC7K325 410T Cấp công nghiệp

DDR3 SDRAMQ: 16GB DDR3, 4GB mỗi thanh, 16bit Data Bit Data Bid SPI Flash: Một thanh 128MBITQSPIFLASH, có thể dùng để lưu trữ file cấu hình FPGA và dữ liệu người dùng. Mức điện áp giao tiếp FPGA Bank: có thể điều chỉnh 1.8V, 2.5V, 3.3V. Nếu cần thay thế mức điện áp, chỉ cần thay thế vị trí tương ứng của hạt từ tính là có thể điều chỉnh được. Nguồn điện của bo mạch lõi: Nguồn điện EEPROM dải 5V-12V; M24C02-WMN6TP dựa trên thiết bị bus I2C. Theo phương pháp khởi động của bo mạch lõi của giao thức dòng thứ hai: hỗ trợ hai chế độ khởi động, đó là JTAG, đầu nối Flash QSPI. Cổng mở rộng, 120 chân, Panasonic AXK5A2137yg MP5700 giao diện SFP tấm đáy: 2 mô-đun quang có thể đạt được truyền thông cáp quang tốc độ cao, lên tới 6GB/giây đồng hồ tấm đáy: 1 đồng hồ tham chiếu 200MHz được kết nối với chân ống đồng hồ MRCC của bo mạch lõi, 1 chân ống đồng hồ GTX tấm đáy của đồng hồ kết nối với bo mạch lõi là cổng mở rộng 40 chân: dành riêng một cổng mở rộng 40 chân cách nhau tiêu chuẩn 2,54mm, được sử dụng để kết nối mô-đun thiết kế riêng của khách hàng. Đồng hồ bo mạch Essence Core: có nhiều nguồn đồng hồ trên bo mạch. Chúng bao gồm đồng hồ hệ thống 200MHz, đồng hồ GTX 125MHz và đồng hồ EMCCLK 66MHz. Cổng JTAG: 10 mũi khâu Cổng JTAG tiêu chuẩn 2,54mm, để tải xuống và gỡ lỗi đèn LED cho chương trình FPGA: tổng cộng 6 đèn LED màu đỏ trên bo mạch lõi, cho biết nguồn điện của thẻ bo mạch, 4 đèn báo tín hiệu và chân ống IO FPGA được kết nối trực tiếp. Phím: 4 phím. 4 phím. Đó là các nút reset FPGA, phím Program_b và hai phím người dùng.

FPGA Xilinx-K7 Kintex7 XC7K325 410T là một mô hình cụ thể của FPGA (Field-Programmable Gate Array) do Xilinx phát triển. Dưới đây là một số thông tin chi tiết chính về FPGA này: Dòng sản phẩm: Kintex-7: FPGA dòng Kintex-7 của Xilinx được thiết kế cho các ứng dụng hiệu suất cao và mang lại sự cân bằng tốt giữa hiệu suất, công suất và giá cả. Thiết bị: XC7K325: Đây là thiết bị cụ thể trong dòng Kintex-7. XC7K325 là một trong những biến thể có sẵn trong dòng sản phẩm này và cung cấp một số thông số kỹ thuật nhất định, bao gồm dung lượng ô logic, lát cắt DSP và số lượng I/O. Dung lượng logic: XC7K325 có dung lượng ô logic là 325.000. Các ô logic là các khối xây dựng có thể lập trình trong FPGA có thể được cấu hình để triển khai các mạch và chức năng kỹ thuật số. Lát cắt DSP: Lát cắt DSP là các tài nguyên phần cứng chuyên dụng trong FPGA được tối ưu hóa cho các tác vụ xử lý tín hiệu số. Số lượng chính xác các lát cắt DSP trong XC7K325 có thể thay đổi tùy thuộc vào biến thể cụ thể. Số lượng I/O: "410T" trong số hiệu model cho biết XC7K325 có tổng cộng 410 chân I/O của người dùng. Các chân này có thể được sử dụng để giao tiếp với các thiết bị bên ngoài hoặc mạch kỹ thuật số khác. Các tính năng khác: FPGA XC7K325 có thể có các tính năng khác, chẳng hạn như khối bộ nhớ tích hợp (BRAM), bộ thu phát tốc độ cao để truyền dữ liệu và nhiều tùy chọn cấu hình khác nhau. Điều quan trọng cần lưu ý là các FPGA như Xilinx-K7 Kintex7 XC7K325 là các thiết bị có thể lập trình cho phép bạn triển khai các mạch kỹ thuật số và chức năng tùy chỉnh bằng cách lập trình các ô logic của chúng. Tính linh hoạt này làm cho chúng phù hợp với nhiều ứng dụng, bao gồm điện toán hiệu năng cao, xử lý tín hiệu số và tăng tốc phần cứng.

Danh mục sản phẩm

-

Điện thoại

-

E-mail

-

Whatsapp

-

Skype

-

Skype

-

Skype